作者:xubin341719(欢迎转载,请注明作者)

7 V' r1 ?5 }$ m# \3 A2 q4 l' L& M/ r6 i2 @+ l4 r

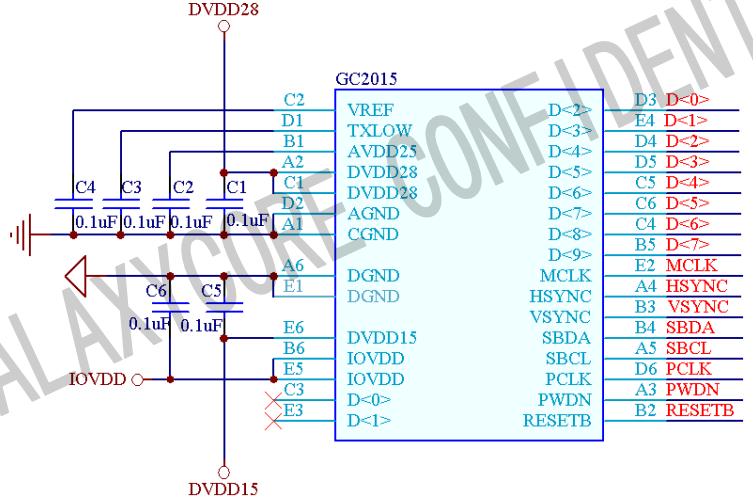

一、摄像头工作原理 上一篇我们讲了摄像头模组的组成,工作原理,做为一种了解。下面我们析摄像头从寄存器角度是怎么工作的。如何阅读摄像头规格书(针对驱动调节时用到关键参数,以GT2005为例)。 规格书,也就是一个器件所有的说明,精确到器件每一个细节,软件关心的寄存器、硬件关心的电气特性、封装等等。单单驱动方面,我们只看对我们有用的方面就可以了,没必要全部看完。主要这样资料全都是鸟语(En),全部看完一方面时间上会用的比较多,找到关键的地方就行了。 1、camera的总体示意图如下:控制部分为摄像头上电、IIC控制接口,数据输出为摄像头拍摄的图传到主控芯片,所有要有data、行场同步和时钟号。GT2005/GT2015是CMOS接口的图像传感器芯片,可以感知外部的视觉信号并将其转换为数字信号并输出。 我们需要通过MCLK给摄像头提供时钟,RESET是复位线,PWDN在摄像头工作时应该始终为低。PCLK是像素时钟,HREF是行参考信号,VSYNC是场同步信号。一旦给摄像头提供了时钟,并且复位摄像头,摄像头就开始工作了,通过HREF,VSYNC和PCLK同步传输数字图像信号。 数据是通过D0~D7这八根数据线并行送出的。

, P& ^& I0 x4 R* S7 H+ w

" c2 ]2 U9 F, _6 Q' w

" c2 ]2 U9 F, _6 Q' w

(1)、Pixel Array GT2005阵列大小为 1268 列、1248 行,有效像素为 1616 列, 1216 行。也就是说摄像头为1600X1200的时候,像素点要多于这个,去除边缘一部分,保证图像质量吧。 (2)、IIC 这个不用说了,摄像头寄存器初始化的数据都从这里传输的,所有的IIC器件都一样的工作,来张图吧,后面做详细分析;

% q7 W1 W) {$ d& n, M5 q下面这一部分在调试驱动的过程中比较重要了:6 A' W# R0 U: k4 O6 T O

(3)、MCLK 电子元件工作都得要个时钟吧,摄像头要工作,这个就是我们所要的时钟,在主控制芯片提供,这个时钟一定要有,要不然摄像头不会工作的。 (4)、上下电时序,这个要接规格书上来,注间PWDN、RESETB这两个脚,不同的摄像头不太一样,这个图是上电时序,上电时参考一下,知道在那里看就行;

) @$ i. ]& z8 j! b, e

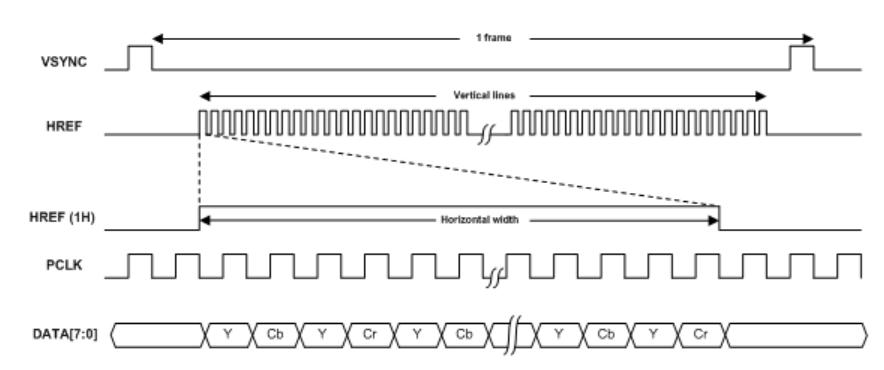

9 {% z* Q4 e3 a) n( n8 T(5)PCLK \D1~D7 摄像头得到的数据要传出来吧,要有数据,当然数据出来要有时钟和同步信号了,看下它的时序,和LCD显示的时序一样,道理是一样的:  , E; ?$ |2 s. Y& z- k2 V( S ` , E; ?$ |2 s. Y& z- k2 V( S `

(6)、主要的寄存器:分辨率、YUV顺序、X轴、Y轴镜相、翻转 ! k- t& Q8 O' l5 @9 @

以上工作完成后,也许还有一些问题,分辨率太小; YUV顺序不对图像不对; XY图像方向。这些工作完成后,如果还有什么细节的问题,如果你想花时间,看规格书里面的寄存器可以解决的,如果不想看,找模组厂的FAE,他们专业的,很快会帮你搞定。 (7)、摄像头的硬件接口

/ W* d u7 S; Z& F

' X3 ^+ r% Y. A

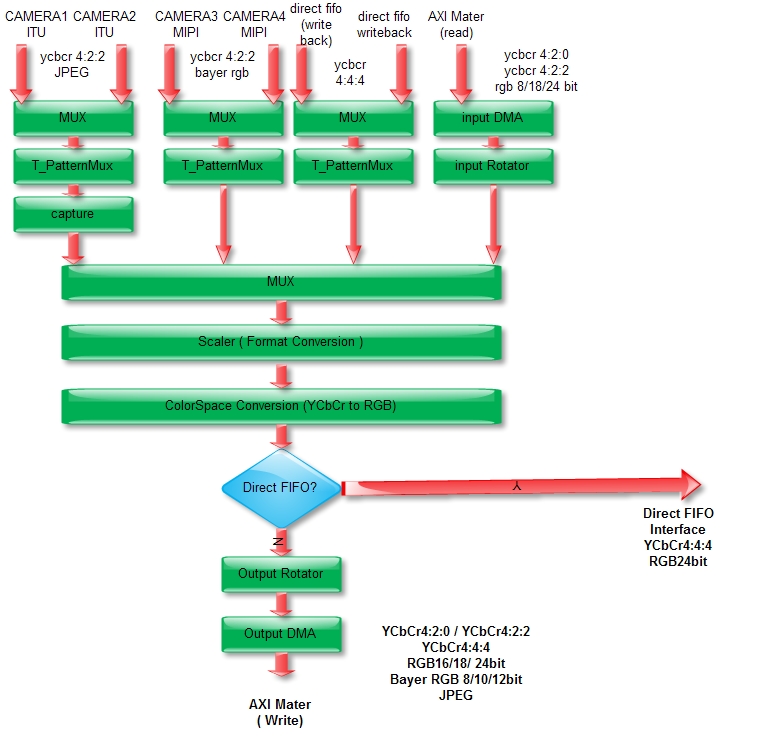

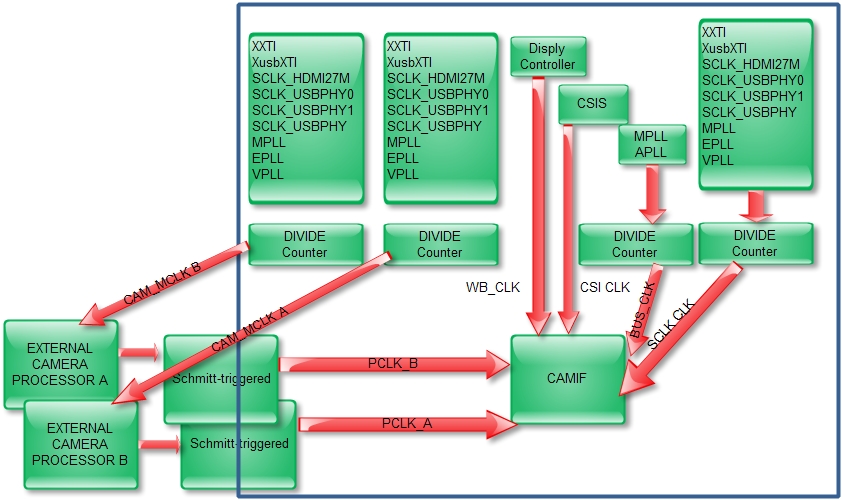

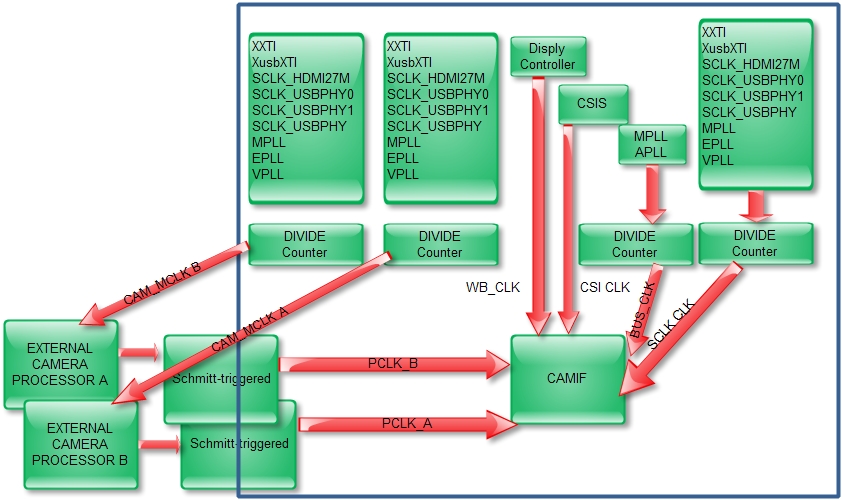

+ [& w. j5 k t$ G! U二、S5pv310上Camera主控芯片上的硬件接口 1、CAMIF Camera Interface 先看一下摄像头接口框图:(这个看着有点抽像,我们放这里,先了解一下,其实驱动中一般不会涉及到这里,不过我们这里分析了,就把这个带出来了)

$ U. t4 D% R) I; ~7 i

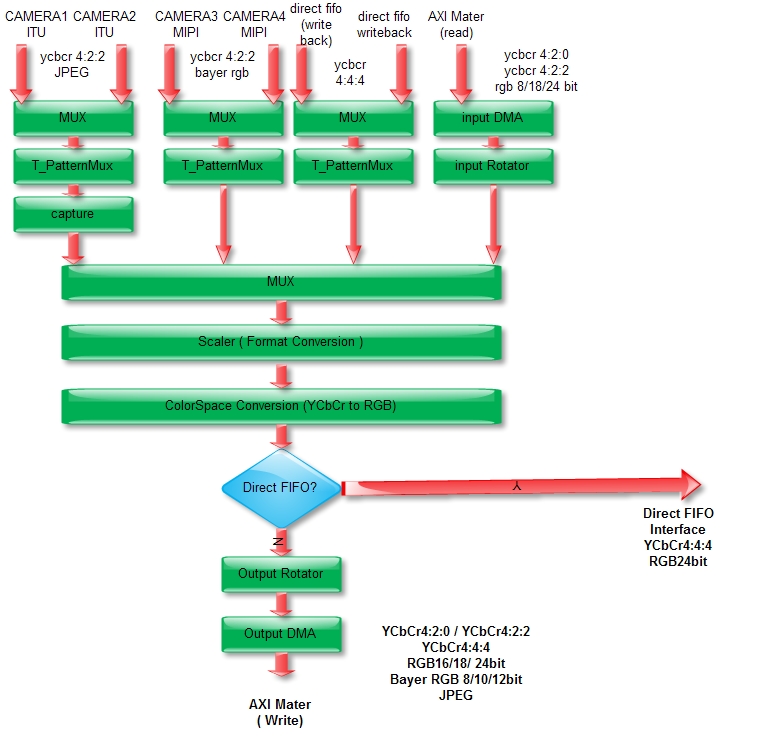

(1)、摄像头接口的主要属性: a、支持多种输入接口:(就是上面我们看到的四模式) DMA (AXI 64-bitinterface) 模式; MIPI (CSI) 模式; ITU-R BT 601/ 656/ 709模式; Direct FIFO (PlayBack)模式; b、支持多种输出模式: DMA (AXI 64-bitinterface) 模式; Direct FIFO 模式; c、支持数码变焦Digital Zoom In (DZI) capability; d、支持多摄像头输入; e、 支持视频同步信号极性可编程控制; f、支持最大输入分辨率为8192X8192; g、支持图像翻转(X轴、Y轴镜相,90、180、270翻转); h、支持多种图片格式; i、支持捕获帧控制; j、支持的图像特效。 2、FIMC Fully InteractiveMobile Camera 摄像头的采集的数据要CPU无法直接处理,主控芯片里面集成了Camera控制器,叫FIMC(FullyInteractive Mobile Camera)。摄像头需要先把图像数据传给控制器,经过控制器处理(裁剪拉升后直接预览或者编码)之后交给CPU处理。实际上摄像头工作需要的时钟(MCLK)也是FIMC给它提供的。 在s5pv310上的摄像头接口是一个FIMC(完全交互式移动相机接口),支持ITUR BT-601-605标准、AMX接口、MIPI接口 MIPI 、ITU、AMX (1)、ITU国际电信联盟无线电通信部门ITU-RRadiocommunication Sector of ITU 简称ITU-RITU-R BT.601 16位数据传输;Y、U、V信号同时传输,是并行数据,行场同步单独输出。

2 D1 ]4 i& j: ]" p9 b% aITU-R BT.6568/10位数据传输;不需要同步信号;串行数据传输;传输速率是601的2倍;先传Y,后传UV。行场同步信号嵌入在数据流中。 (2)、MIPI(移动行业处理器接口)是MobileIndustry Processor Interface的缩写 MIPI 规范:Camera工作组:MIPI Camera Serial Interface 1.0specification .Camera Serial Interface 2 v1.0 (CSI-2) (3)、AMX(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller BusArchitecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。 3、接口信息 FIMC信号定义如下所示(YCbCr模式) Signal | I/O | Description | Type& @2 S0 g/ @4 t, K

| HREF | I | 行同步信号 | | PCLK | I | 像素时钟 | DATA[7:0] | I | 像素数据 | FIELD | O | FIELD信号 | | MCLK | O | 系统时钟信号 |

通过CAM_MCLK给摄像头提供时钟,RST是复位线,PWDN在摄像头工作时应该始终为低。HREF是行参考信号,PCLK是像素时钟,VSYNC是场同步信号。一旦给摄像头提供了时钟,并且复位摄像头,摄像头就开始工作了,通过HREF,PCLK和VSYNC同步传输数字图像信号。数据是通过DATA0~DATA7这八根数据线并行送出的。

3 C& ~5 p$ E! L4、不同接口模式的工作时序 ITU-R BT 656输入时序图,这种方式下同步信号已经内嵌到视频数据中了,因此不需要额外的行和帧同步信号。

" C; u w" n+ \8 W ?# b" G# H

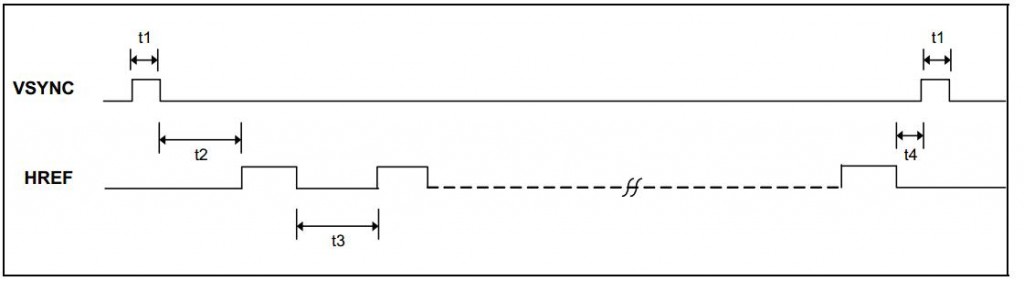

7 G* |# _$ \! m2 E: xITU-R BT 601输入时序图,这种方式下行和帧同步信号独立于视频数据,因此需要同步信号。

0 }2 a" {8 E; V8 Y5 ~, F

* S' L* Q; e& {

; z+ R4 y+ q7 {2 i5 o: t1 a

(ITU-R BT 601: 16位数据传输;21芯;Y、U、V信号同时传输。

w5 G$ r# E: _$ U; g7 MITU-R BT 656: 9芯,不需要同步信号;8位数据传输;串行视频传输;传输速率是601的2倍;先传Y,后传UV。) 同步信号的时延参数 Ø t1:表示VSYNC前、后插入周期 Ø t2:表示HREF前插入周期 Ø t3:表示 HREF宽度 Ø t4:表示HREF后插入周期 1 I: N+ p2 n0 Y: A) u0 i7 t8 k6 y

5、camera的时钟域,三个时钟:系统时钟、PCLK、MCLK 每个摄像头接口包括三个时钟域,每一个时钟域是系统总线时钟,第二个是摄像头像素时钟PCLK,第三个时钟域为内部时钟MCLK。系统总线时钟必需高于PCLK, CAM_MCLK 必需固定频率分频,如PLL时钟。如果有外部时钟晶振,CAM_MCLK 空掉。不需要同步MMCLK,PCLK应该与schmitt-triggered电平移位器连接。  8 h$ p9 H+ z5 O' ^ 8 h$ p9 H+ z5 O' ^

! j& b I, s5 f( N

6、硬件接口电路 主控芯片上的接口:  2 W1 j4 w- i# y$ X 2 W1 j4 w- i# y$ X

2 k( ?1 i' @" ?0 M; gcamera 接口  " @, F- J, G; Y " @, F- J, G; Y

% {5 G5 Z9 N5 ~1 k: a

+ ]( ^, [! _/ z( @* w7 n

|

|站点统计|小黑屋|手机版|Archiver|摄像头模组论坛网-摄像头方案网CCM99

( 粤ICP备18155214号 )

|站点统计|小黑屋|手机版|Archiver|摄像头模组论坛网-摄像头方案网CCM99

( 粤ICP备18155214号 )

窥视卡

窥视卡 雷达卡

雷达卡 发表于 2015-8-12 10:17:03

发表于 2015-8-12 10:17:03

8 h$ p9 H+ z5 O' ^

8 h$ p9 H+ z5 O' ^

提升卡

提升卡 置顶卡

置顶卡 沉默卡

沉默卡 喧嚣卡

喧嚣卡 变色卡

变色卡 千斤顶

千斤顶 显身卡

显身卡 发表于 2015-11-4 13:23:20

发表于 2015-11-4 13:23:20

楼主

楼主